Cortex M4 Vector Table

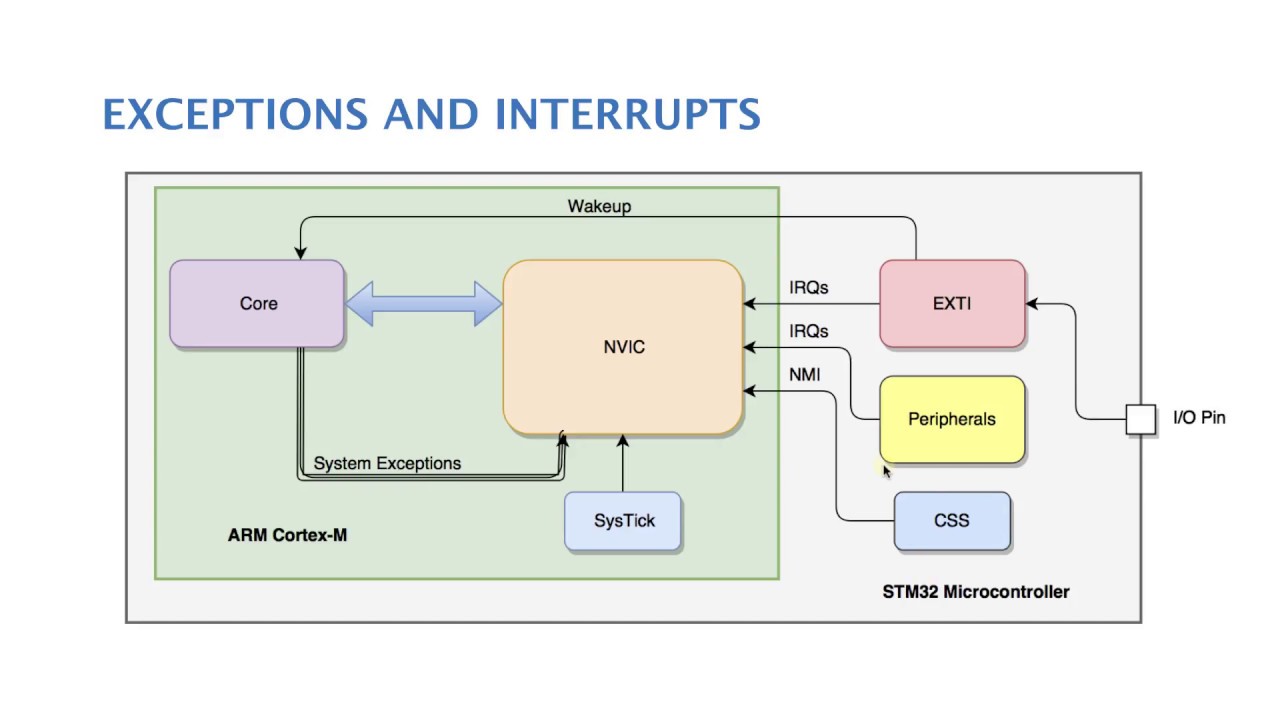

Some of the spaces in the vector table are not used because the Cortex-M0 only has a few system exceptions.

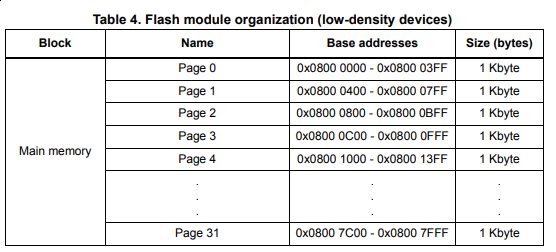

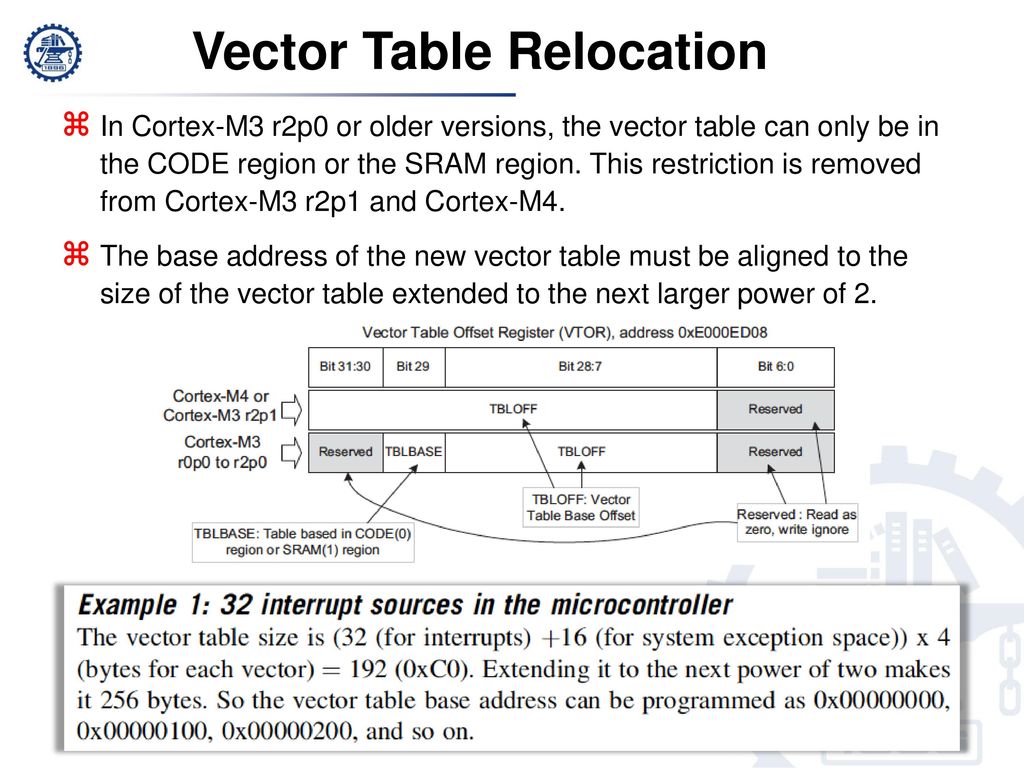

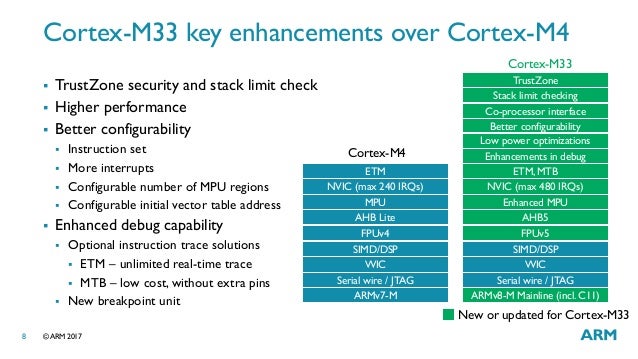

Cortex m4 vector table. STM32 Cortex®-M4 MCUs and MPUs programming manual Introduction This programming manual provides information for application and system-level software developers. 10 New 69 CatB Rare Store immediate overlapping exception return operation might vector to incorrect interrupt 01 Apr 13:. The details in this Technical Note applies to Cortex-M cores with the VTOR register.

The rest of the Vector Table, starting at Index 1, holds Exception Handler pointers. The cores consist of the Cortex-M0, Cortex-M0+, Cortex-M1, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33, Cortex-M35P, Cortex-M55. From reading through the NRF522 datasheet it states that 38 are actually used, this is also backed up within nrf52.h.

Table 1 Categorization of errata Errata Type Definition Category A. Recall that the Exception Number maps to an offset within the Vector Table. Vector Table Offset Register:.

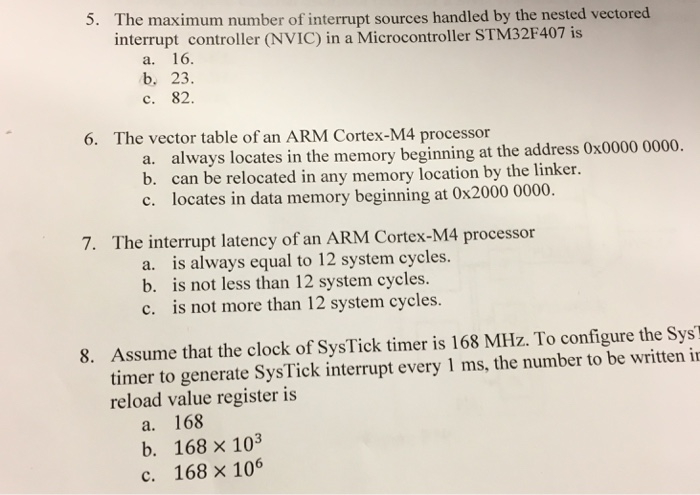

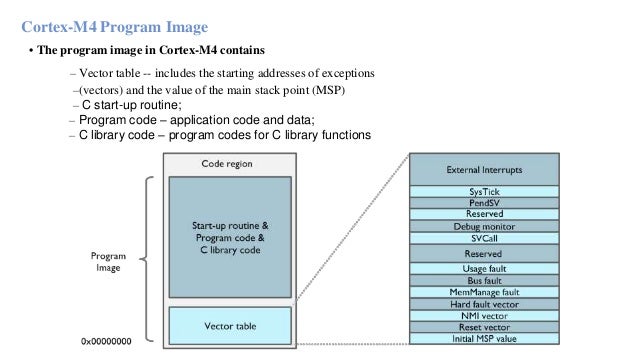

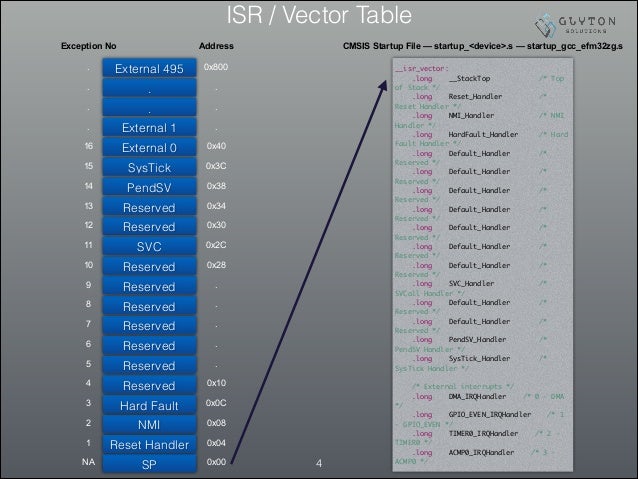

– C start-up routine;. Cmake cpp11 hal startup cortex-m4 cortex-m3 interrupt-handers vector-table Updated Oct 25, 17;. And then it loads the Program counter with the address available at offset 4 and starts executing.

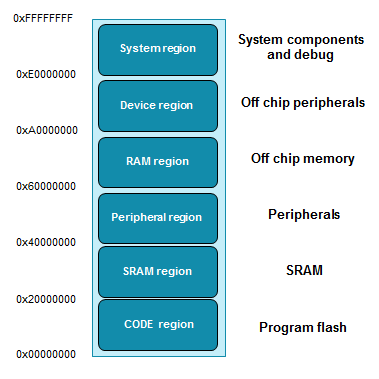

This is a 7-bit aligned address (so its 7 LSBs must be zero) which points to the location of this interrupt vector table. Cortex M Vector Table. Beyond the reset entry point (0x), the exception table also contains the software entries table used by the NVIC to branch the software.

– user May 4 '13 at 0:49. In general, the vector table is fixed at address 0x on system reset. Now I would like to copy the vector table and the.

Cortex-M3 (and higher) has the VTOR register. – Program code – application code and data;. Another solution is to edit the linker-script and reserve enough space for a vector table there.

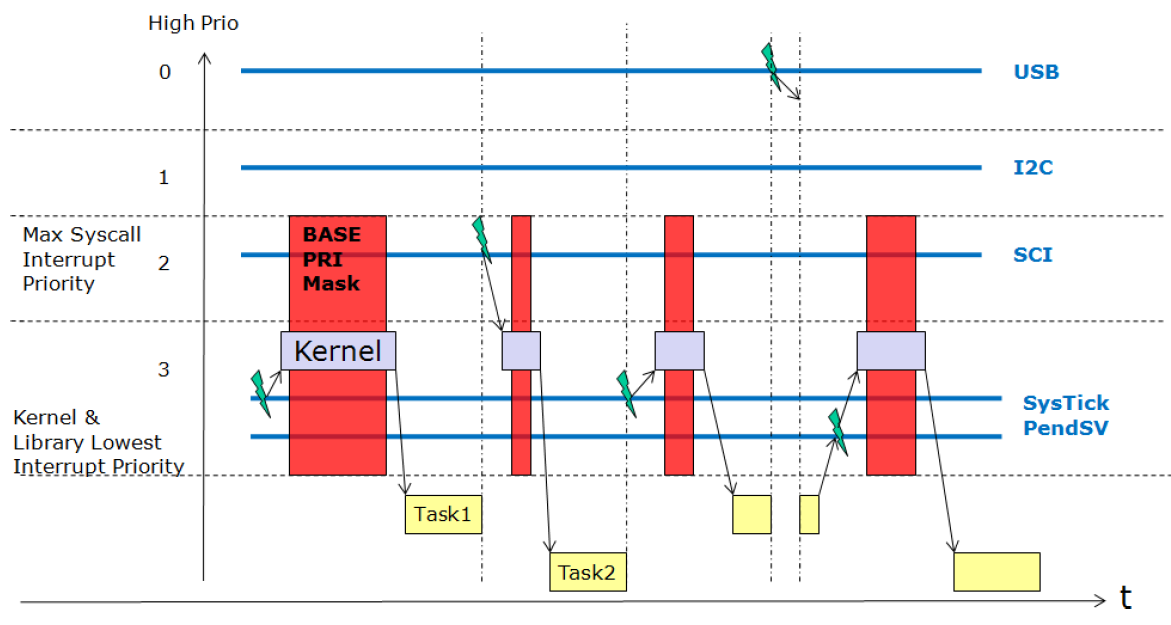

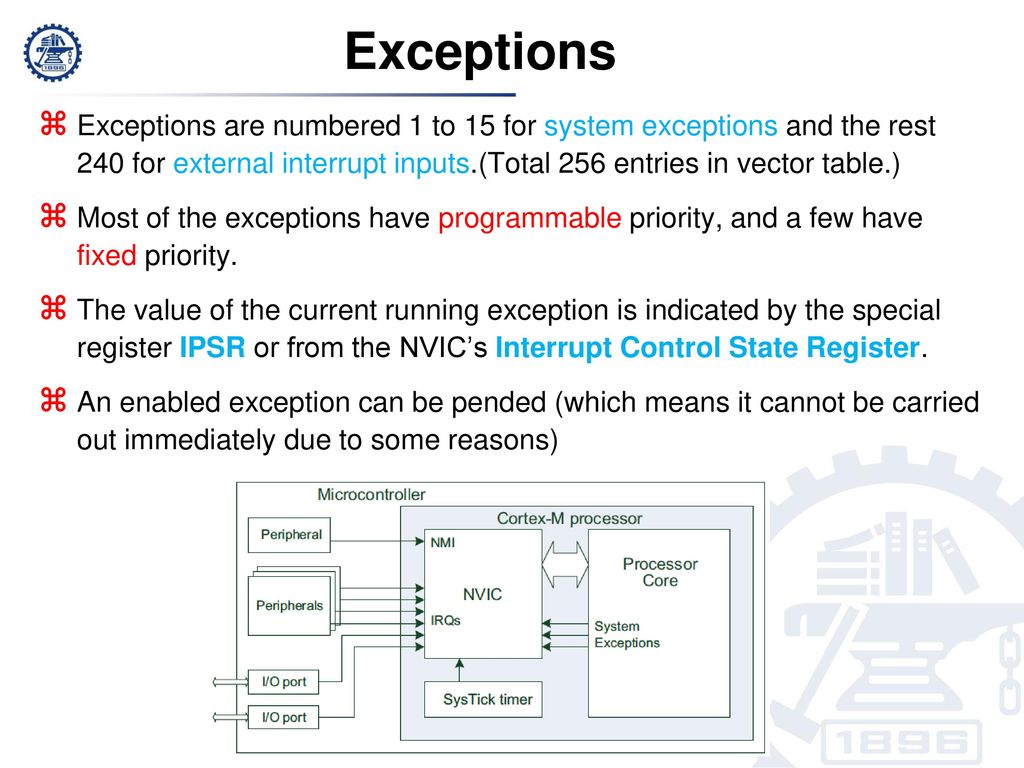

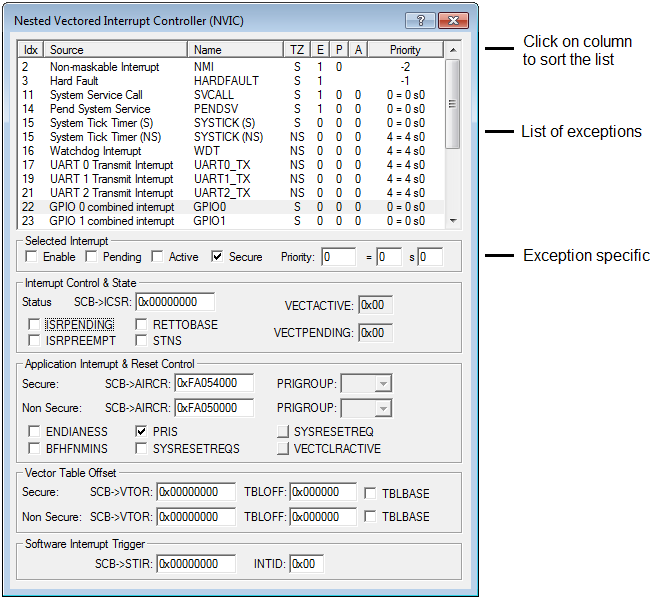

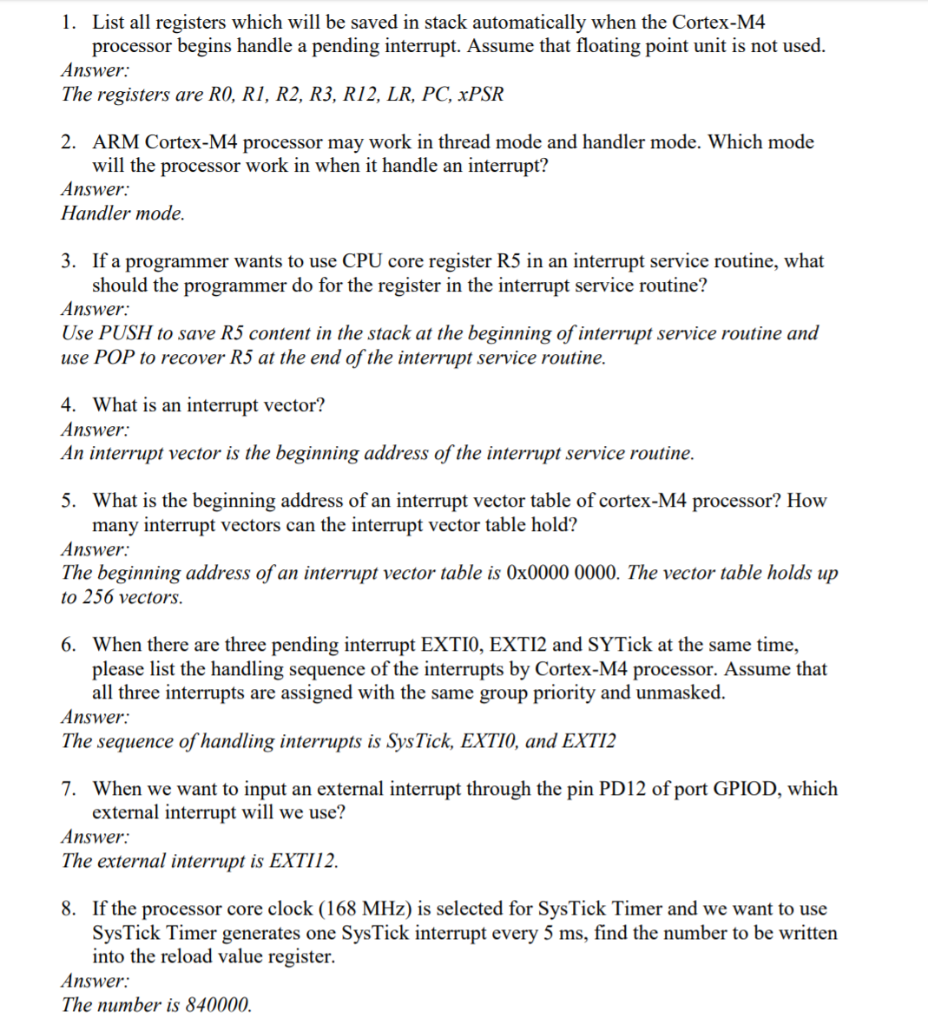

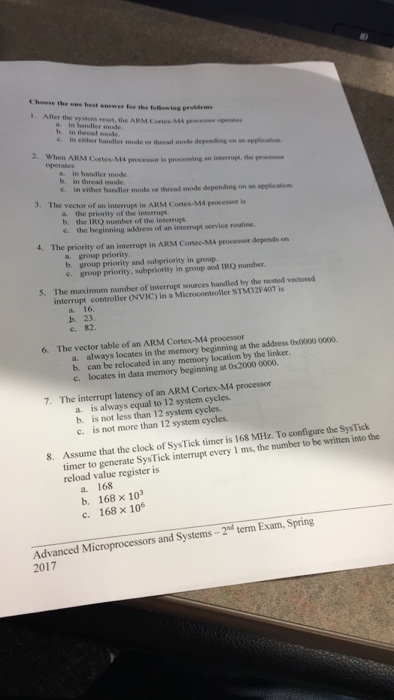

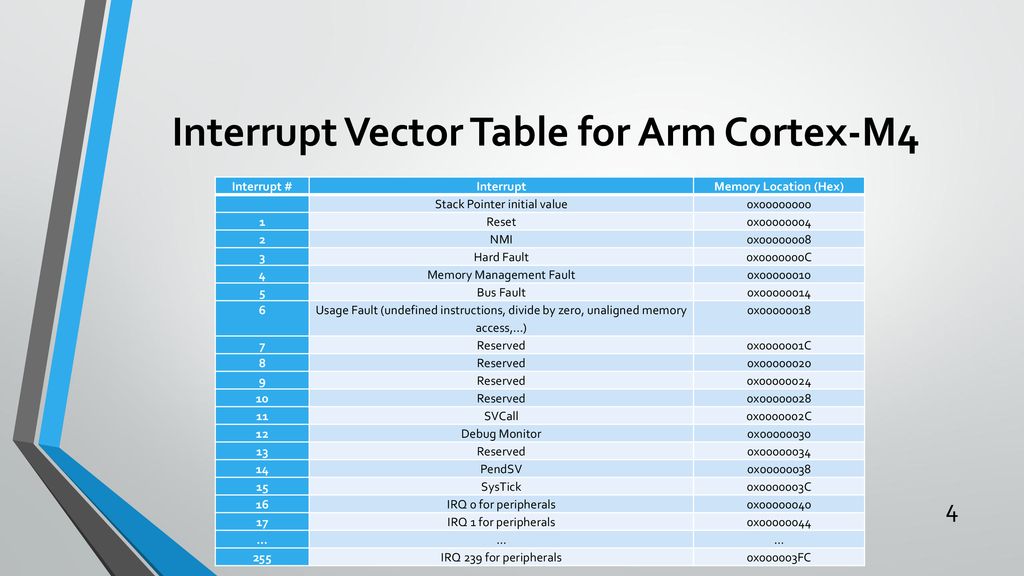

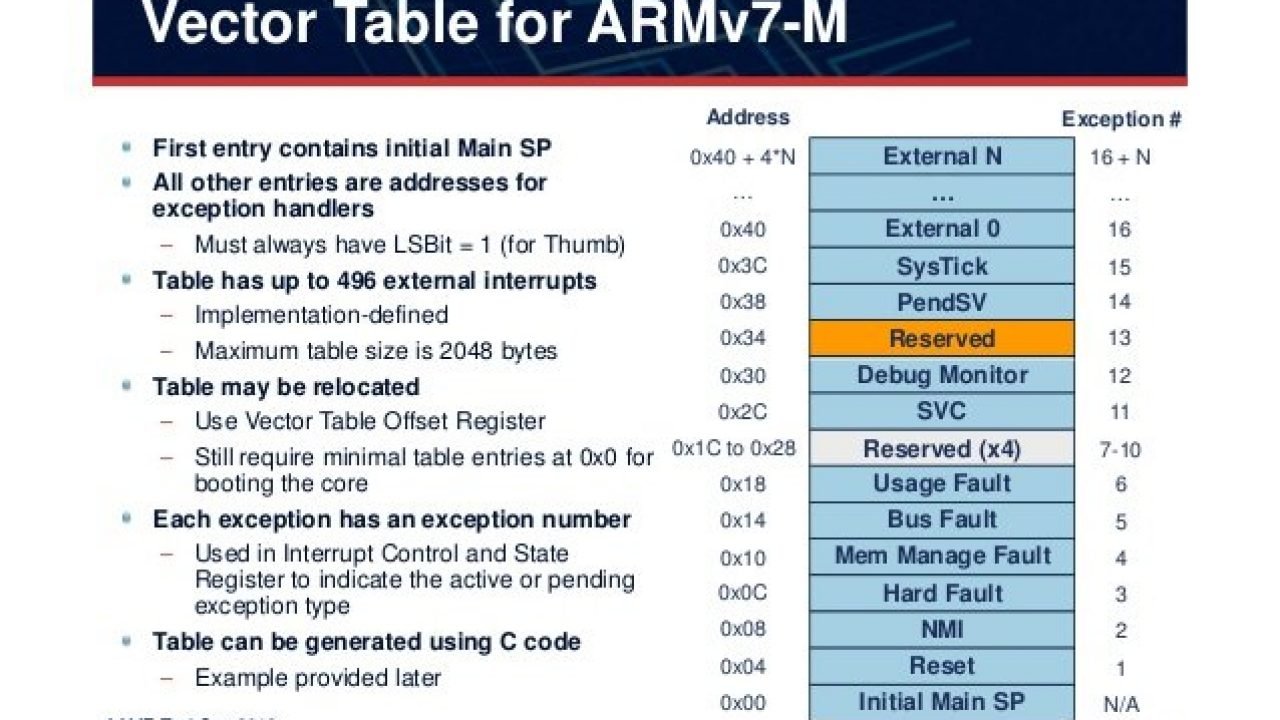

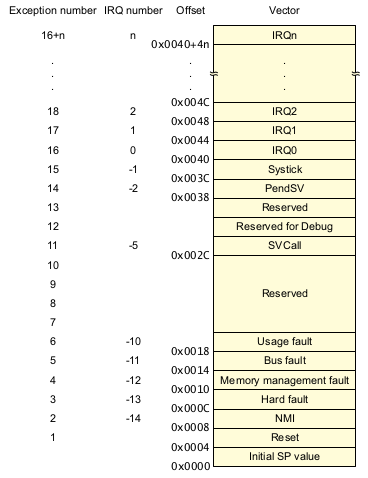

Nested Vector Interrupt Controller. It gives a full description of the STM32 Cortex®-M4 processor programming model, instruction set and core peripherals. Basics of Exceptions Cortex-M4 Core Peripherals › System Control Block (SCB) xSCB Registers › SysTick Timer xRegisters xConfiguration xCode Example › Nested Vectored Interrupt Controller (NVIC) xException/Interrupt Vector Table xException States xNVIC Registers.

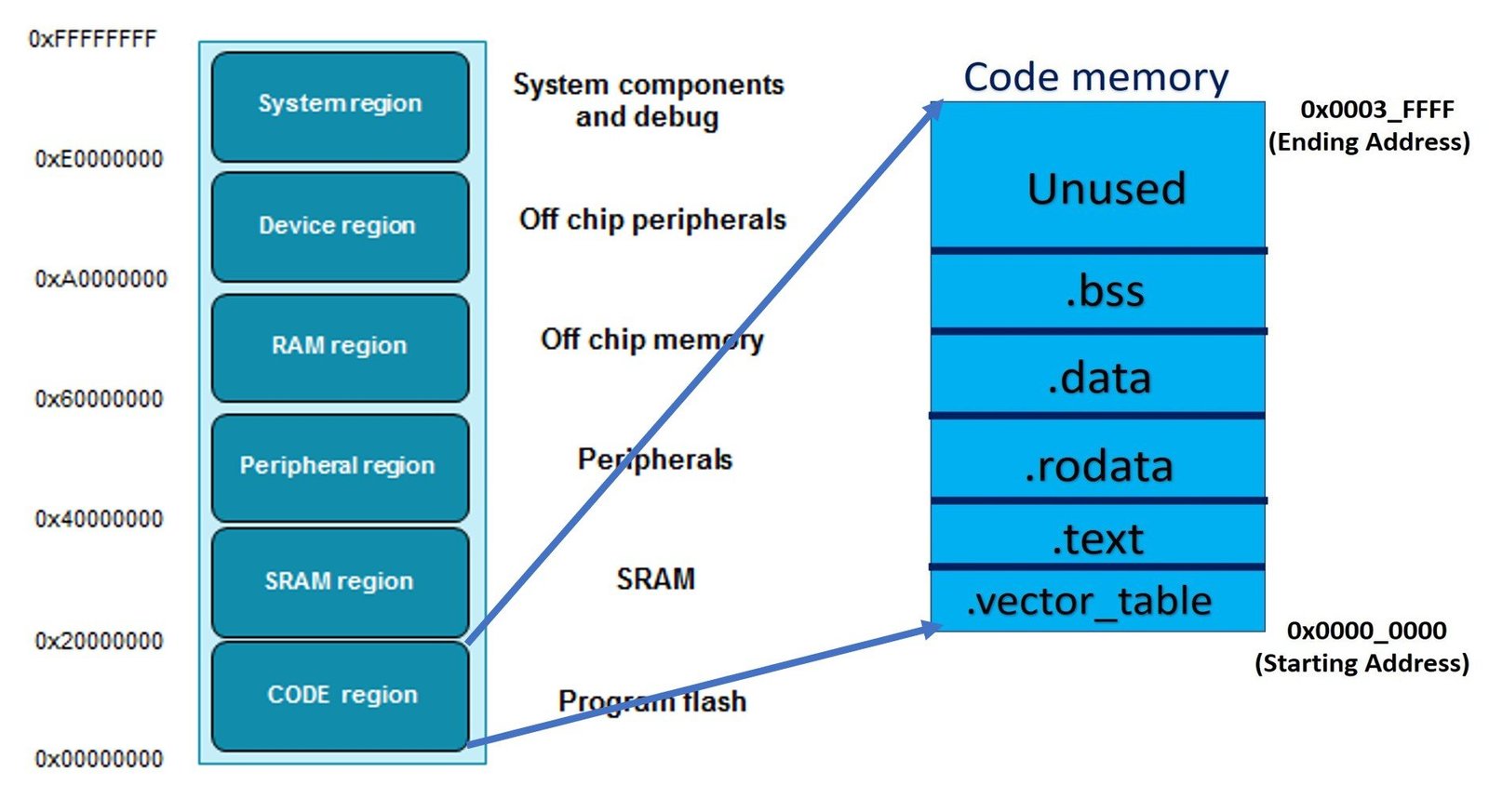

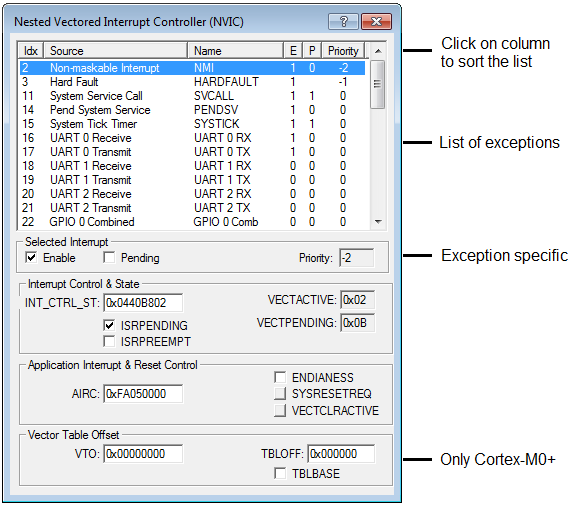

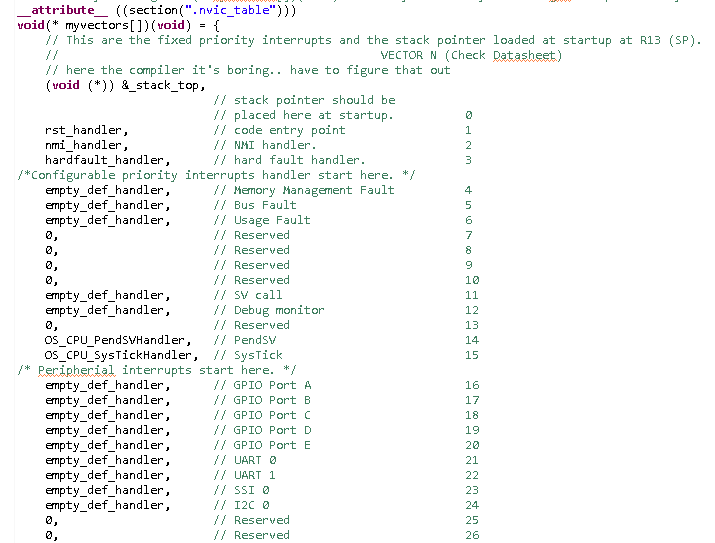

On the ARM Cortex-M4 the first entry into the vector table holds the initialization value for the stackpointer, which is automatically loaded into the CPU's stackpointer register upon reset. This would explain why this bit has to be set accordingly, telling the core to use the system bus and access the SRAM. The Vector Table is located by default in 0x0 (aliased at flash start 0x) and there is where the linker places all exception handler addresses (which include interrupts).

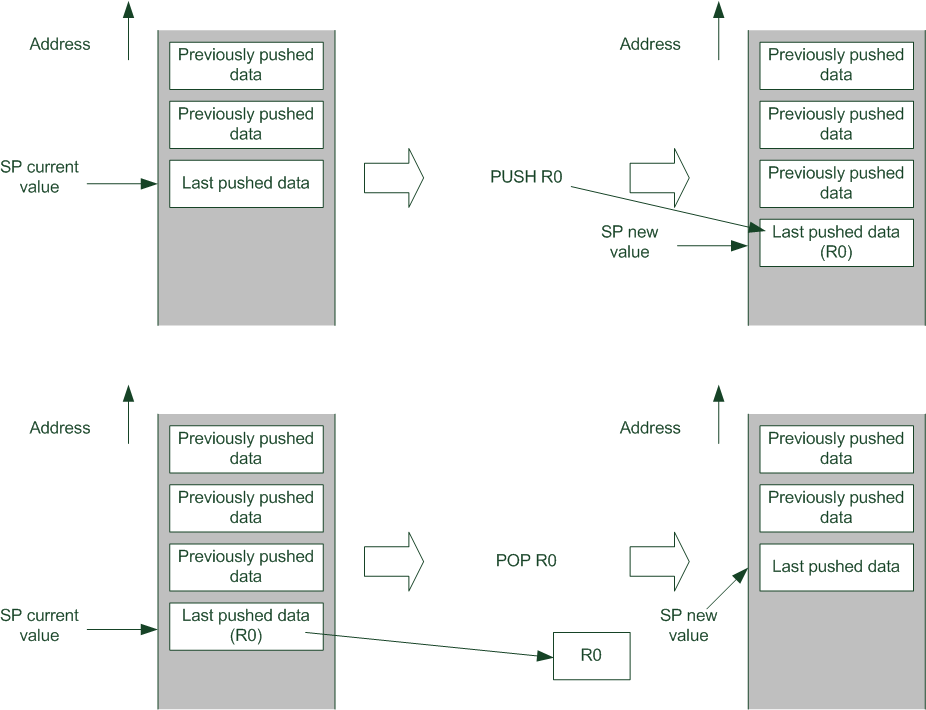

It is typically located at the beginning of the program memory, however Using Interrupt Vector Remap it can be relocated to RAM. Cortex-M4 Program Image ECE 5655/4655 Real-Time DSP 3–11 Cortex-M4 Program Image † The program image in Cortex-M4 contains – Vector table -- includes the starting addresses of exceptions (vectors) and the value of the main stack point (MSP);. The ARM core, up on boot up, loads the stack pointer with the value stored at offset 0.

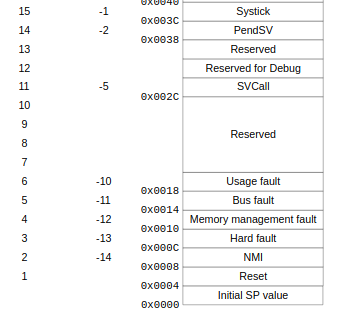

Below can the last one can be seen. Because the Kinetis MCU family RAM starts at 0x1fff0000, this bit must be cleared" but it sl. Cortex -M4®Vector Table After reset, vector table is located at address 0 Each entry contains the address of the function to be executed The value in address 0x00 is used as starting address of the Main Stack Pointer (MSP).

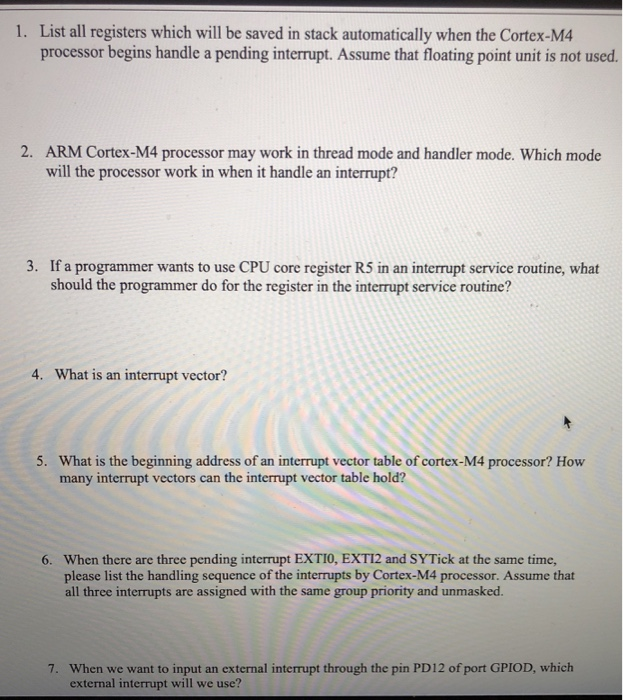

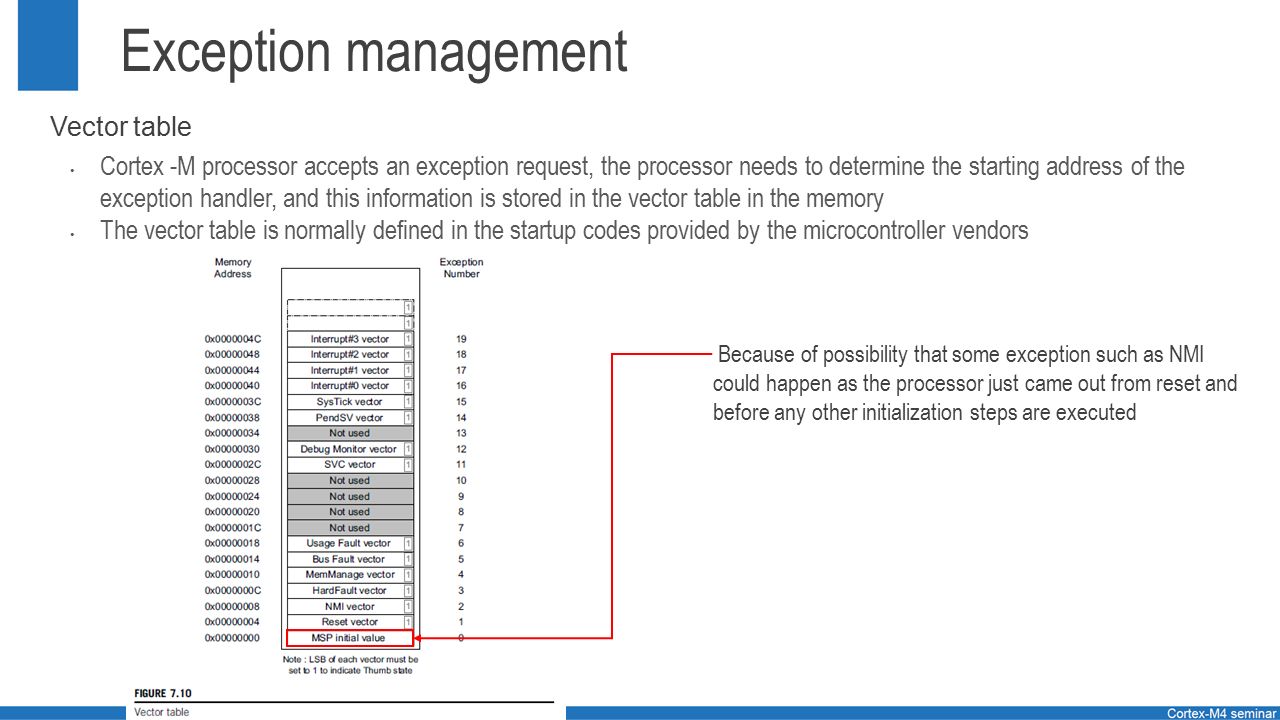

Each exception has an associated 32-bit vector that stores the memory location where the ISR that handles the exception is located. As stated by the Cortex M4 reference manual states that a system can have 0+ seperate handlers within the vector table. To that of a digital signal processor than the Cortex®-M4 core.

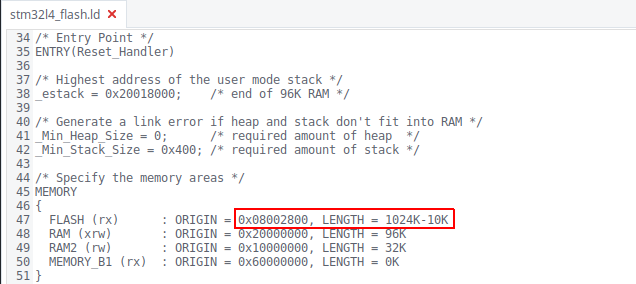

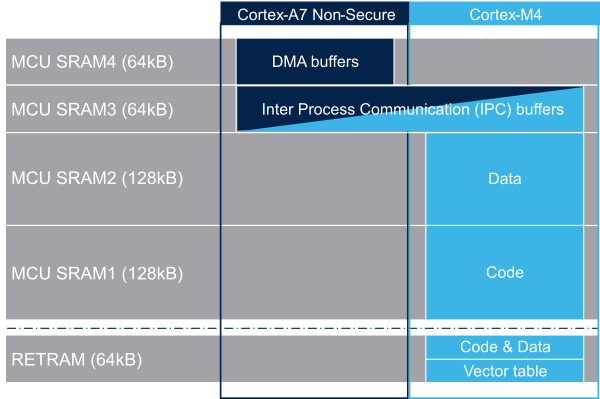

ARM Cortex-M4 User Guide (Interrupts, exceptions, NVIC) Sections 2.1.4, 2.3 – Exceptions and interrupts. The vector table provides the initial value for the Main Stack Point and the reset vector address. The Cortex-M4 vector table is mapped from address 0x (so to the RETRAM) at reset, but it can be remapped by software to any other location by means of the vector table offset register (VTOR).

The applicable products are listed in the table below. See the example project for more details. Special note to ARM Cortex-M users:.

For example, the Cortex-M3 and Cortex-M4 processors have an interrupt latency of only 12 clock cycles. Each vector has 4 bytes, containing a branching instruction in one of the following forms:. Changes in Document v1.

The interrupt latency of the Cortex-M series processor is quite low and is deterministic. FPU_IRQn = 38 /*!< 38 FPU. App_vector { readonly section .APP };.

The Cortex-M0 core lacks a Vector Table Offset Register. Vector table of ARM Cortex_M4 That vector table will contain all the locations of the exception and interrupt ISR. The reason for my suggestion is that as your program grows, it might allocate variables that overwrite the vector table, as variables get allocated.

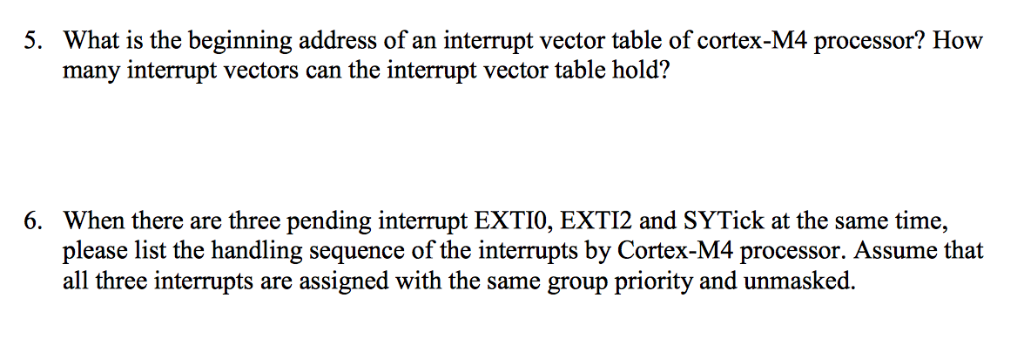

The Nested Vectored Interrupt Controller dialog (for Cortex-M3, Cortex-M4, and Cortex-M7) shows the status of all exceptions. It contains the starting address of all exception handlers. For Cortex-M4 processor, exceptions include resets, software interrupts and hardware interrupts.

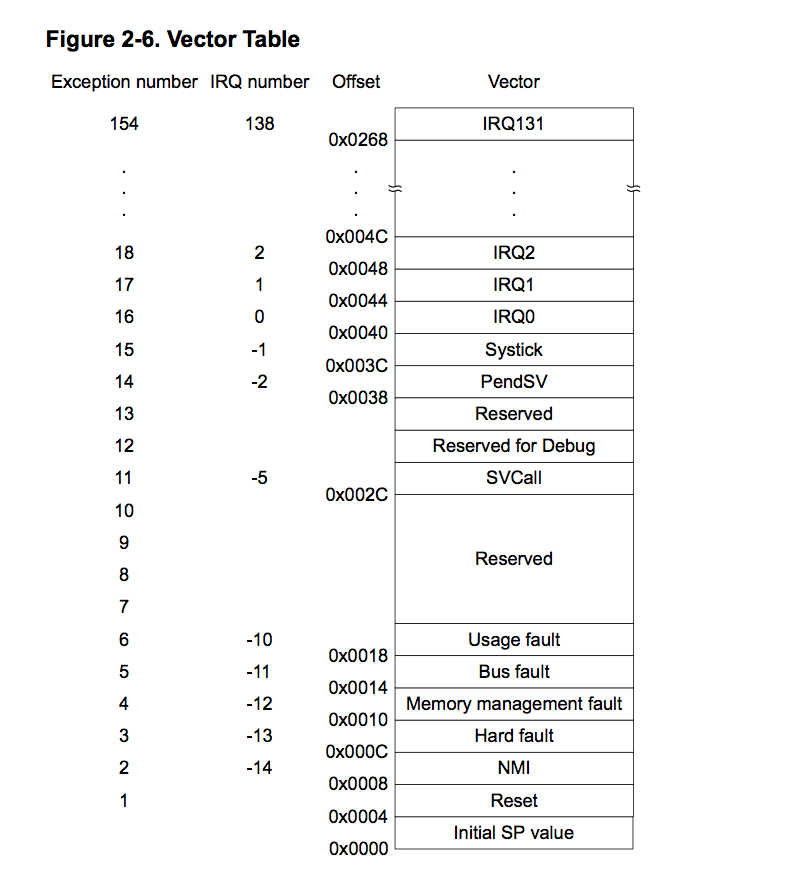

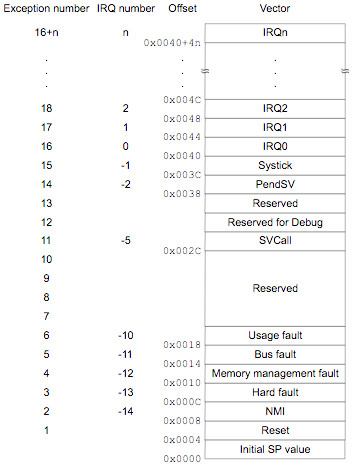

Figure below shows the order of the Cortex-M4 exception and interrupt vectors in the vector table. When a project is created in IAR workbench the start up code and vector table are in assembly files. Now I would like to copy the vector table and the.

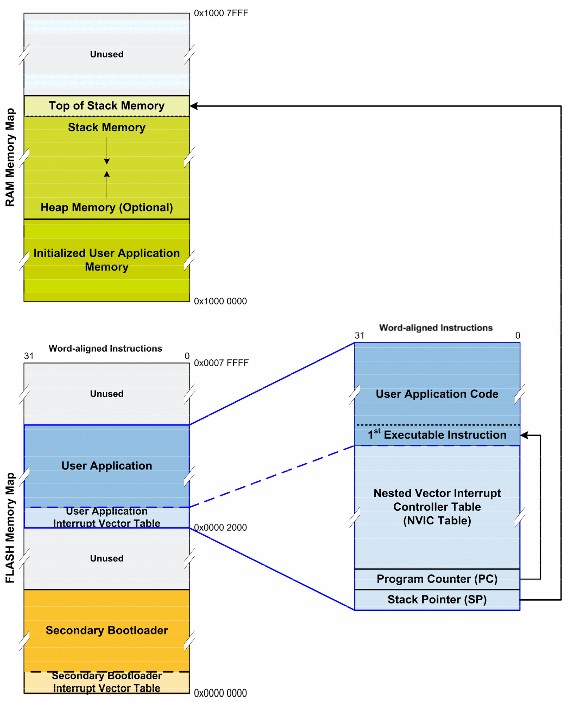

As Cortex-M4 has below exceptions, interrupts and those things are ordered in the below image. After reset, the bootloader gets started first and, if a valid user program is present, it is the bootloader's responsibility to start the user program. The vector table in ARM Cortex M series looks like:.

As we have discussed in the last section, the vector table contains the address of the ISR routines of all interrupts and exceptions that the microcontroller supports. Lnls-dig / openMMC Star 16 Code Issues Pull requests Open source firmware for MMC controllers. `SystemInit()` is provided by the silicon vendor, and may vary largely from device to device.

The Cortex-M4 core implements the VTOR, but we will not use it. The interrupt vector table has eight entries. After reset, the bootloader gets started first and, if a valid user program is present, it is the bootloaders responsibility to start the user program.

Cortex-M0+, Cortex-M3 and Cortex-M4 processors:. Vdm-dev / stm32. It said " The Cortex-M4 assumes the RAM starts at 0x and expects the vector table to be stored in that address if the VTOR TBLBASE29 bit is set.

Vector table The vector table contains the reset value of the stack pointer, and the start addresses for all exception and interrupt handlers. You can select and configure (where applicable) each exception using the following control groups:. Upon encountering a B instruction, the ARM processor will jump immediately to the address given by adr, and will resume execution from there.The adr in the branch instruction is an offset from the current value of the program counter (PC) register.

In Cortex-M7, Cortex-M23 and Cortex-M33 processors:. Cortex-M4 & Cortex-M4 with FPU Software Developers Errata Notice. The vector table can be populated directly with the FreeRTOS defined xPortSysTickHandler(), xPortPendSVHandler() and vPortSVCHandler() functions respectively, or.

Some of the unused exceptions are used on other ARM processors like the Cortex-M3/M4 processor, as these processors have additional system exceptions. The Cortex ® -M4 with FPU CPU always fetches the reset vector on the ICode bus. In some ARM Cortex architectures (I know at least the ARM Cortex-M0+, ARM Cortex-M3, and ARM Cortex-M4 support this) there is a register located at address 0xE000ED08 called the “Vector Table Offset Register”.

If you are using a M3/M4 device, yes, if you. Index 0 of the Vector Table holds the reset value of the Main stack pointer. If you check the datasheet of TM4C123G ARM Cortex M4 microcontroller, it has 15 system exceptions and 138 peripheral interrupts.

As you can see, the interrupt vector table is an array of memory addresses. For each exception, the dialog shows the number, source, name, state, and priority. Interrupt vectors and vector table Interrupt masks and priorities Cortex Nested Vectored Interrupt Controller (NVIC).

The symbol __Vectors is the address of the vector table in the startup code and the register SCB->VTOR holds the start address of the vector table. By default the vector table is located in the starting of the memory map (address 0x0). The same applies to the relationship between Cortex-M4/M7 and other Cortex-M processors;.

The ARM Cortex-M specifications reserve Exception Numbers 1-15, inclusive, for these. Cmake ipmi freertos cortex-m3 mtca Updated Jun 25, ;. The Vector Table defines the entry addresses of the processor exceptions and the device specific interrupts.

ARM Cortex-M3, ARM Cortex-M4 and ARM Cortex-M4F ports need FreeRTOS handlers to be installed on the SysTick, PendSV and SVCCall interrupt vectors. Maybe on an interrupt the ICode bus is used, which cannot access the SRAM even when remapped (I don't know if this is true). On the ARM Cortex-M4 the first entry into the vector table holds the initialization value for the stackpointer, which is automatically loaded into the CPU's stackpointer register upon reset.

I am using GNU ARM Eclipse and the generated project structure using newlib for the initialization. Instructions available on Cortex-M0/M0+/M1/M3 can run on a Cortex-M4/M7. IAR workbench vector table ARM CortexM4 0 I am developping a firmware on an ARM CORTEX M4 processor, with IAR IDE (v7.71).

The project can be tested using the C-SPY Simulator driver or on a STM32 target device, using I-jet. Typically, on power-on reset, the Vector table base address is defined to be at 0. Furthermore, each interrupt/exception also has a unique interrupt number assigned to it.

So, 0x address contains initial Stack Pointer Value. The figure below shows the interrupt vector table of the ARM Cortex-M4 microcontroller. The default value for VTOR is defined by chip designers.

The ARM Cortex-M is a group of 32-bit RISC ARM processor cores licensed by Arm Holdings.These cores are optimized for low-cost and energy-efficient microcontrollers, which have been embedded in tens of billions of consumer devices. Relocating interrupt vector table to RAM on ARM Cortex-M0 Hello there, I've been trying to develop a simple bootloader on Keil uVision5 for a custom microcontroller my university is building, and we use a Cortex-M0, with no VTOR register (unlike M0+, M3 and M4) and a vector table fixed at address 0x00_00. Can be the case for the vector table, the interrupt service routines and certain time-critical control loops that are executed often and require low latency and deterministic execution time.

What Is Nested Vector Interrupt Control Nvic

Arm Cortex M3 Boot Process Programmer Sought

Embedded Security 3 Immutable Boot Code Kickstart Embedded

Cortex M4 Vector Table のギャラリー

A Practical Guide To Arm Cortex M Exception Handling Interrupt

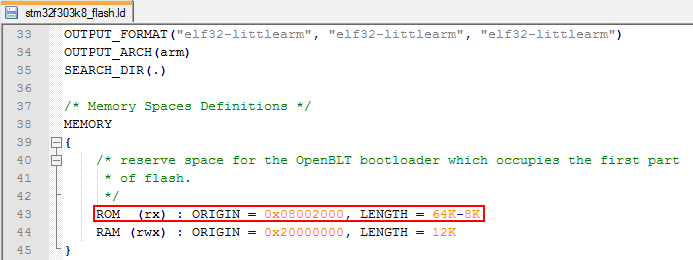

Manual Ports Armcm4 Stm32 Openblt Bootloader

Manual Ports Armcm4 Stm32l4 Openblt Bootloader

How Much Stack Memory Do Cortex M Applications Need Processors Blog Processors Arm Community

Stm32mp15 Ram Mapping Stm32mpu

Interrupt Vector Table An Overview Sciencedirect Topics

Exception Vector An Overview Sciencedirect Topics

Developing A Generic Hard Fault Handler For Arm Cortex M3 Cortex M4 Ppt Video Online Download

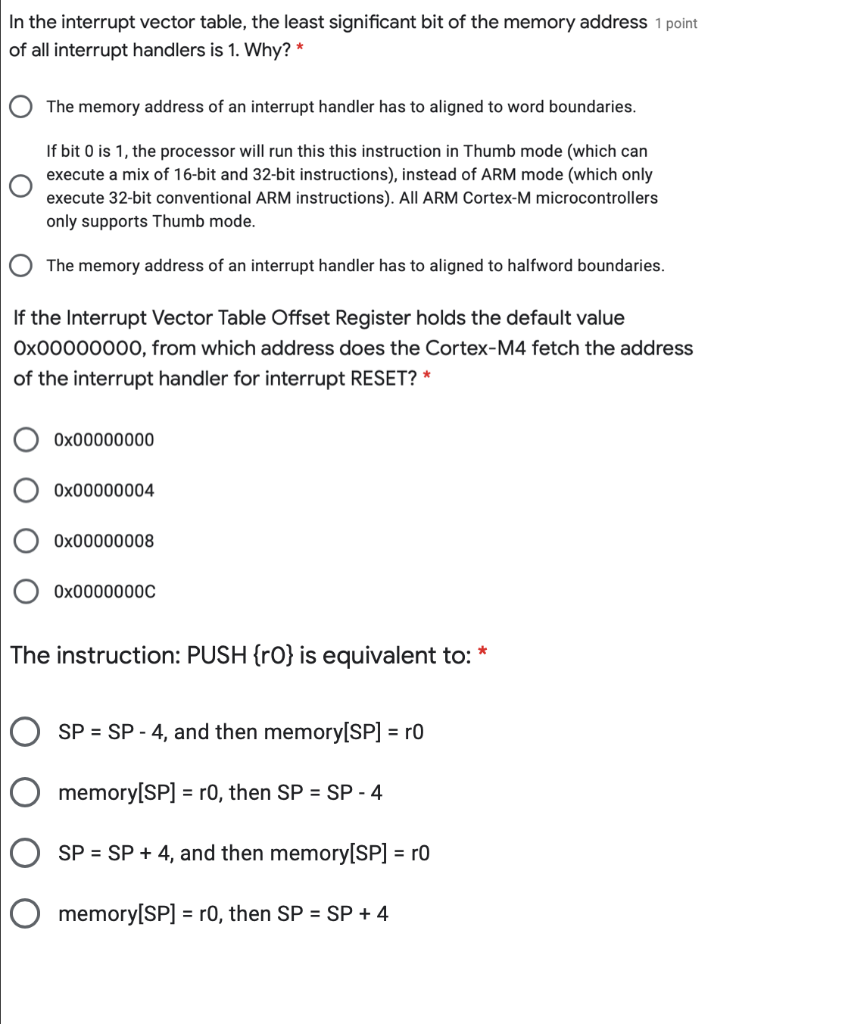

Solved In The Interrupt Vector Table The Least Significa Chegg Com

Manual Ports Armcm4 Stm32f3 Openblt Bootloader

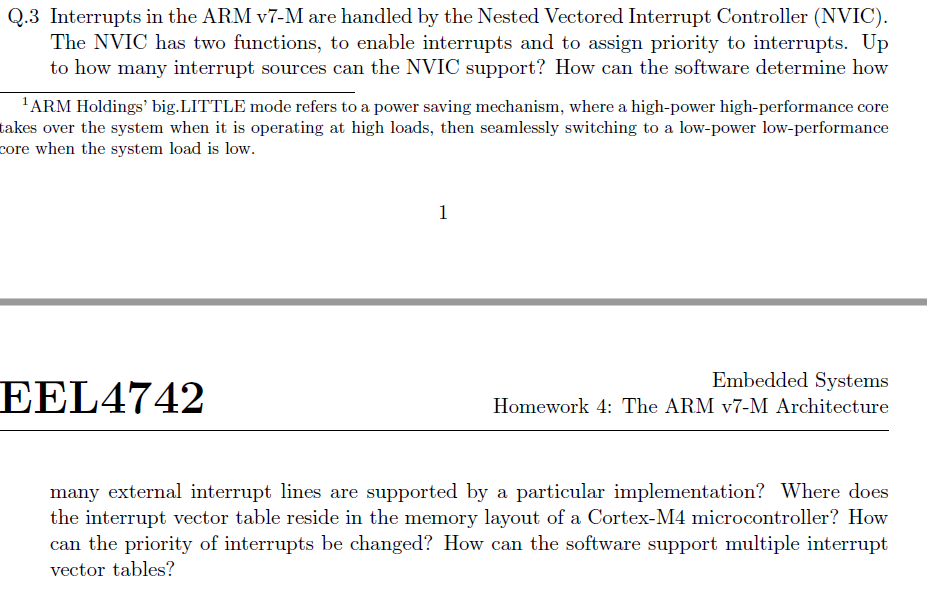

Interrupts In The Ar M V7 M Are Handled By The Nes Chegg Com

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

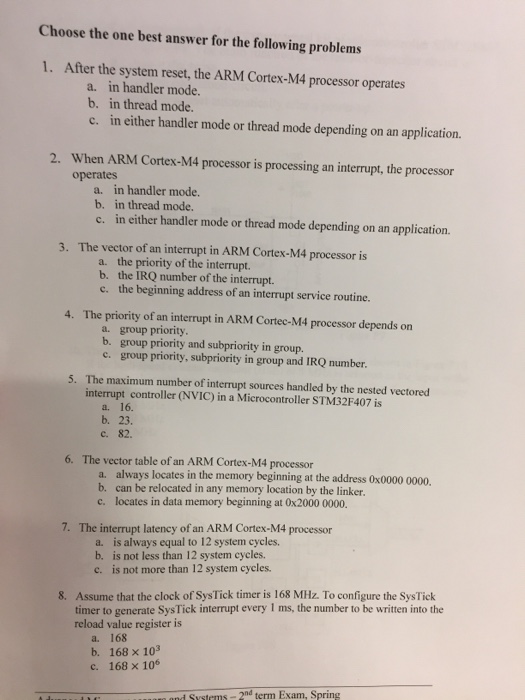

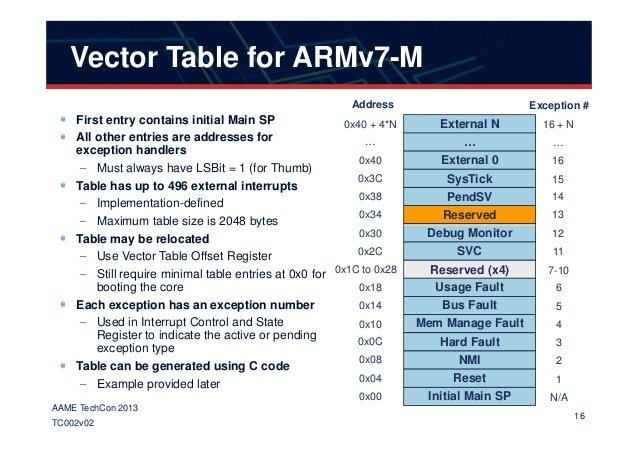

Solved After The System Reset The Arm Cortex M4 Processo Chegg Com

Reset Vector An Overview Sciencedirect Topics

Context Switching In Arm Cortex M3 M4 Wisesciencewise

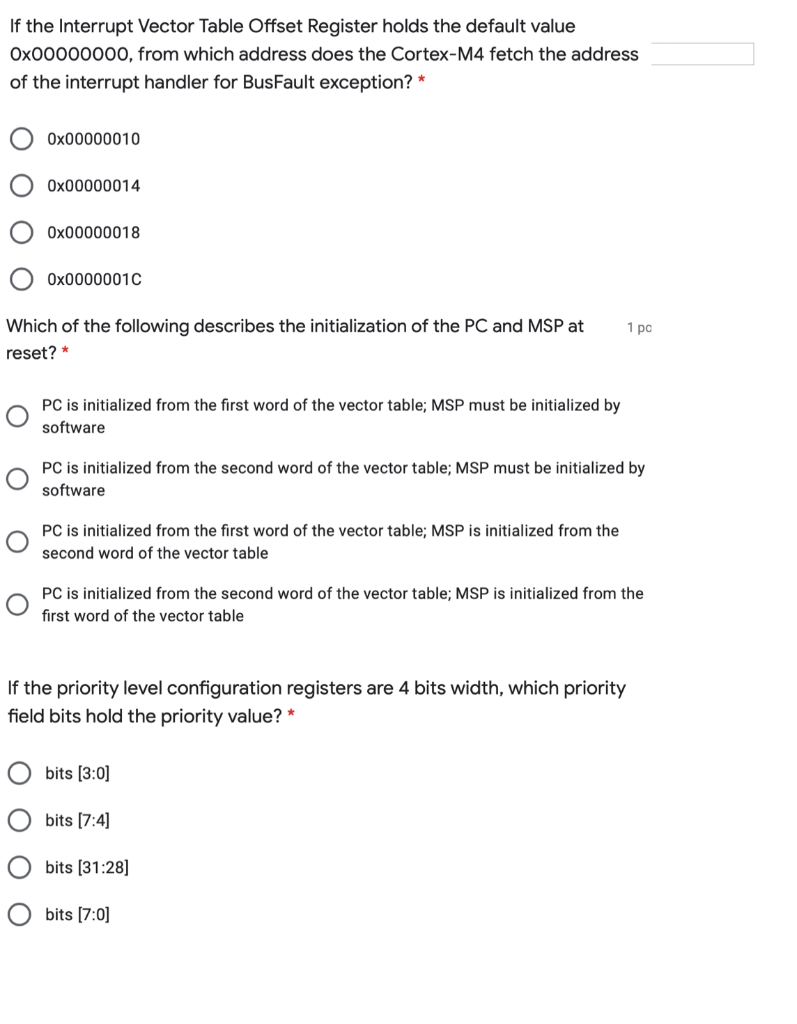

Solved If The Interrupt Vector Table Offset Register Hold Chegg Com

Cortex M3 Devices Generic User Guide

Arm Cortex M Interrupts And Freertos Part 3 Dzone Iot

Http Wiki Csie Ncku Edu Tw Embedded 15q1w4 Interrupt Part2 Pdf

Analyzing Arm Cortex Based Mcu Firmwares Using Binary Ninja Kudelski Security Research

Arm Explains Good Interrupt Control For Low Power Processors

Manual Ports Armcm4 Tm4c Openblt Bootloader

Reset Vector An Overview Sciencedirect Topics

Refer To Chapter 7 8 9 In The Reference Book Ppt Download

6 2il Kvfjj Fm

Interrupt Vector Table An Overview Sciencedirect Topics

Refer To Chapter 7 8 9 In The Reference Book Ppt Download

Arm Cortex M Interrupts And Freertos Part 3 Dzone Iot

Primary And Secondary Bootloaders For Cortex M Processors Valpont

Arm Cortex M Ngắt Va Freertos Phần 1

Software Development In Ar Mv8 M Architecture Yiu

Beginner Guide On Interrupt Latency And Arm Cortex M Processors Processors Blog Processors Arm Community

Solved De 25k D How Does The Interrupt Vector Table Wor Chegg Com

Debugging Hard Faults On Arm Cortex M Mcu On Eclipse

Exception Vector An Overview Sciencedirect Topics

µvision User S Guide Nested Vector Interrupt Controller

Embedded Gadgets Lab Initialization Of Armv8 M Trustzone Secure

Http Ccrs Hanyang Ac Kr Webpage Limdj Embedded Cortex M Pdf

List All Registers Which Will Be Saved In Stack Au Chegg Com

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

Interrupt Vector Address In Program Counter Electrical Engineering Stack Exchange

How To Debug A Hardfault On An Arm Cortex M Mcu Interrupt

Q Tbn 3aand9gcs8iwbzu3szxefzcr7 Lggahhodowj8zgebge5omrrgt4bvyqqc Usqp Cau

Exception Vector An Overview Sciencedirect Topics

1 List All Registers Which Will Be Saved In Stack Chegg Com

Q Tbn 3aand9gcs8iwbzu3szxefzcr7 Lggahhodowj8zgebge5omrrgt4bvyqqc Usqp Cau

Q Tbn 3aand9gcthk Fktoozdlakl7g 9yqie 4pizqjky8rjpzqzydcidhif1ip Usqp Cau

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Priority Register An Overview Sciencedirect Topics

Cortex M4 Technical Reference Manual

Solved After The System Reset In Arm When Arm Certex M4 Chegg Com

الدرس ٩ Arm Cortex M4 Nested Vectored Interrupt Controller Nvic Youtube

Manual Ports Armcm4 Stm32 Openblt Bootloader

Interrupt Handling In Arm Cortex M Embien Technology Blog

Arm Cortex M Interrupts And Freertos Part 3 Dzone Iot

Reverse Engineering Of Arm Microcontrollers Rado Rc1 Security Hardware Reversing

Cortex M0 Vector Table Avr Freaks

Manual Ports Armcm4 Tm4c Openblt Bootloader

A Deeper Look At The Stm32f4 Project Template Getting Things Started Charles Korn

Multiple Cortex M Processing Cores Valpont

Analyzing Arm Cortex Based Mcu Firmwares Using Binary Ninja Kudelski Security Research

Debugging Hard Faults On Arm Cortex M Mcu On Eclipse

Interrupt Vector Address In Program Counter Electrical Engineering Stack Exchange

Solved The Maximum Number Of Interrupt Sources Handled By Chegg Com

Arm Cortex M4 Programmer Model

Exceptions And Interrupts Chap 7 8 Tae Min Hwang Ppt Download

Arm Cortex M Interrupts And Freertos Part 3 Dzone Iot

Arm How To Write A Bootloader

Arm Cortex M Wikipedia

Interrupt Management Rt Thread Document Center

00xnor Sergey Ostrikov Cortex M4 Core Registers

A Practical Guide To Arm Cortex M Exception Handling Interrupt

5 What Is The Beginning Address Of An Interrupt V Chegg Com

Understand The Gnu Assembler Startup File Of Cortex M4

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

A Practical Guide To Arm Cortex M Exception Handling Interrupt

µvision User S Guide Nested Vector Interrupt Controller

Interrupt And Exception Programming Ppt Download

Cmsis Core Device Templates

07 Startup Code Vector Table Nclabmd

Systick Timer Interrupt Programming Tm4c123 Arm Cortex M4

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Interrupt Vector Table An Overview Sciencedirect Topics

Interrupt Vector Table An Overview Sciencedirect Topics

A Practical Guide To Arm Cortex M Exception Handling Interrupt

Exception Vector An Overview Sciencedirect Topics

Tock Embedded Operating System Walkthrough

6 2il Kvfjj Fm

Arm Cortex M Bootup Cmsis Part 2 3

07 Startup Code Vector Table Nclabmd

Arm Cortex M3 Boot Process Programmer Sought

Www Eng Auburn Edu Nelsovp Courses Elec22 Slides Interrupt Io part2 Pdf

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

Handler Mode An Overview Sciencedirect Topics

Interrupt Vector Table An Overview Sciencedirect Topics

Lecture 9 Interrupts Youtube

Porting Ucosiii On Cortex M4 Lm4f1xl Other Microcontrollers Forum Other Microcontrollers Ti E2e Support Forums

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

Interrupt Management Rt Thread Document Center

Q Tbn 3aand9gcqbffhdnzfhr2 Olk6j Qddpzkufior36wfjwabz8omalznfaqs Usqp Cau

Arm Cortex M Wikipedia